# ON THE EFFECT OF OP-AMP FINITE GAIN IN DELTA-SIGMA MODULATORS

# Adrian Leuciuc and Cristian Mitrea

Department of Electrical and Computer Engineering State University of New York at Stony Brook Stony Brook, NY 11794-2350

#### ABSTRACT

Abstract: The effect of finite gain of op-amps in both discrete-time (switched-capacitor) and continuous-time  $(G_m-C)$  implementations of Delta-Sigma modulators is studied. It is shown that a continuous-time realization is less sensitive to finite gain of op-amps. Specifying a maximum admissible drop in the SNR due to the finite gain of op-amps, the values of these gains for each of the delta-sigma integrating stages can be determined. The results are obtained using the linear model for the quantizer and are validated by performing direct simulations of the delta-sigma modulators.

### 1. INTRODUCTION

The effect of finite gain of op-amps on the performances of delta-sigma modulators has been intensively studied. Most of the analyses have been performed for the switch-capacitor (SC) implementations and it has been considered that the only effect of the finite gain is introducing leakage in the discrete-time integrator [1], [2]. A more accurate analysis shows that the gain of the SC integrator is altered as well [3], [4]. Therefore the drop in the SNR is larger then predicted. In this communication we will show how to determine the necessary gains for the op-amps or OTAs ensuring a maximum preset drop of the SNR. Multiple sets of values will meet this requirement. The decision which set of gains for the op-amps in the integrating stages of the delta-sigma modulator should be adopted for a specific topology depends on some other optimization parameters: circuit complexity, power dissipation, settling time, linearity, and so on. However, one rule to follow is to chose the minimum values for these gains, especially when the modulator is to be realized for a low-voltage application and high-gain stages are difficult and expensive to obtain.

# 2. THE EFFECT OF OP-AMP FINITE GAINS ON THE INTEGRATORS

### 2.1. SC integrators

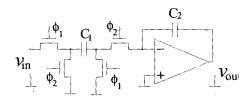

A SC integrator is depicted in Fig. 1. If the op-amp is ideal, the transfer function of the circuit is

$$T_d(z) = \frac{C_1/C_2}{z-1} = \frac{k_d}{z-1},$$

(1)

describing a non-inverting integrator with delay.

Figure 1. Non-inverting SC integrator with delay

If we take into consideration the finite gain of the op-amp,  $A_0$ , the transfer function of the circuit in Fig. 1 becomes

$$\tilde{T}_{d}(z) = \frac{\tilde{k}_{d}}{z - (1 - \alpha)},\tag{2}$$

where  $\tilde{k}_d$  and  $\alpha$  are given by

$$\tilde{k}_d = \frac{k_d}{1 + \frac{1}{A_0} (1 + k_d)}$$

$$\alpha = \frac{\tilde{k}_d}{A_0} \approx \frac{k_d}{A_0}.$$

(3)

It can be easily observed that, besides introducing leakage, the gain of the integrator is altered. The analysis of the inverting, delay-free SC integrator, leads to identical expressions (3) for the modified gain and leakage coefficient. As it will be shown later, besides the drop in the SNR due to the leaky integrators, the change in integrator gains decreases furthermore the performances of the modulator.

For continuous-time realizations of delta-sigma modulators, two approaches can be used: active-RC (or MOSFET-C) and  $G_m-C$  implementations. Basically, the effect of the op-amp finite gain on the ideal transfer function of such integrators is almost the same, excepting the fact that a high-frequency, right-half plane zero appears in the case of active-RC realization. In the following the  $G_m-C$  approach will be considered, the obtained results being valid for the other case as well. A  $G_m-C$  integrator is depicted in Fig. 2. If the output resistance of the operational transconductance amplifier (OTA) is infinite, the transfer function of the circuit is

$$T_{c}(s) = \frac{G_{m}/C}{s} = \frac{k_{c}}{s}.$$

$$V_{in} \qquad C \qquad V_{ou}$$

$$(4)$$

Figure 2.  $G_m - C$  continuous-time integrator

Considering the finite output resistance of OTA,  $R_{out}$ , the following transfer function results

$$\tilde{T}_c(s) = \frac{k_c}{s + \omega_0},\tag{5}$$

where  $\omega_0$  is given by

$$\omega_0 = \frac{1}{CR_{out}} = \frac{k_c}{A_0} \tag{6}$$

with  $A_0 = G_m R_{out}$ , the open circuit voltage gain of OTA. It can be seen that in the case of the continuous-time integrator the influence of the op-amp finite gain consists only in generating leakage.

To make a comparison between the effects of the op-amp finite gain on the SC and  $G_m-C$  integrators, let us compute the magnitude square of their frequency responses. From (2) it results

$$\left| \tilde{T}_d \left( e^{j\omega} \right) \right|^2 = \frac{\tilde{k}_d^2}{\left| e^{j\omega} - 1 + \alpha \right|^2} \approx \frac{\tilde{k}_d^2}{\omega^2 + \alpha^2}, \text{ for } \omega \ll 1.$$

(7)

whereas for the continuous-time one we have

$$\left|\tilde{T}_c(j\omega)\right|^2 = \frac{k_c^2}{\omega^2 + \omega_0^2}.$$

(8)

Comparing the expressions of the leakage coefficients for the two integrators, (3) and (6), it can be easily seen that the effect of the finite gain of op-amps is quantitatively the same. However, for the SC integrator the time constant is also affected and therefore the drop in the SNR for a SC delta-sigma modulator will be larger compared to a continuous-time realization.

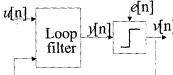

### 3. STATE SPACE DESCRIPTION

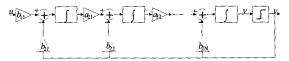

After seeing the local effect of op-amp finite gain, let us analyze how this affects globally the performances of the  $\Delta\Sigma$  modulator. A general block scheme for a  $\Delta\Sigma$  modulator is depicted in Fig. 3. Since continuous-time modulators are more difficult to analyze and simulate and taking into account that we can always obtain their discrete-time equivalents [5], in the following we will consider only the discrete-time case. However, when comparing the effects of op-amp finite gain in the SC and  $G_m-C$  modulators, we have to keep in mind that continuous-time integrators have only leakage, whereas the SC capacitor ones have also non-ideal gains. The state-space description of the discrete-time  $\Delta\Sigma$  modulator is

$$\mathbf{x}[n] = \mathbf{A}\mathbf{x}[n-1] + \mathbf{b}_1 u[n] + \mathbf{b}_2 v[n]$$

$$y[n] = \mathbf{c}^T \mathbf{x}[n] + du[n]$$

$$v[n] = sign(y[n]) = y[n] + e[n].$$

$$\mathbf{u}[\mathbf{n}]$$

$$\mathbf{v}[\mathbf{n}] = \mathbf{v}[\mathbf{n}]$$

Figure 3. General structure of a  $\Delta\Sigma$  modulator

Considering the linear model for the quantizer, that is replacing it with an adder, the noise transfer function  $H\left(z\right)$  can be computed as

$$H(z) = \frac{V(z)}{E(z)} = \frac{1}{1 + \mathbf{c}^T (z\mathbf{I} - \mathbf{A})^{-1} \mathbf{b}_2}.$$

(10)

If the integrators within the  $\Delta\Sigma$  modulator have leakage, the modified state matrix  $\tilde{\bf A}$  can be obtained from  ${\bf A}$  by subtracting from its main diagonal the leakage coefficients  $\alpha_i$  for each integrating stage. The modified gains of the integrators can also be introduced in the state matrix expression. For a topology containing only integrators with delay, one has to multiply the  $i^{th}$  column, excepting the term  $a_{ii}$ , with the corresponding ratio  $\tilde{k}_d/k_d$ . The state-to-output vector  ${\bf c}$  has also to be modified accordingly. This way, the new noise transfer function  $\tilde{H}(z)$  can be determined using a similar expression as (10). The in-band noise power in the case of ideal op-amps can be computed as

$$P_e = \sigma_e^2 \int_0^{\pi/R} \left| H\left(e^{j\omega}\right) \right|^2 d\omega \tag{11}$$

and the corresponding value for finite gain op-amps is

$$\tilde{P}_{e} = \sigma_{e}^{2} \int_{0}^{\pi/R} \left| \tilde{H} \left( e^{j\omega} \right) \right|^{2} d\omega. \tag{12}$$

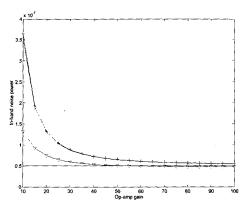

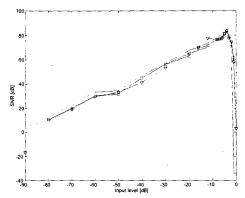

Figure 4. In-band noise power for a SC modulator as a function of op-amp gains:  $\nabla$  - first stage,  $\diamond$  - second stage, + - third stage, no markers - ideal case.

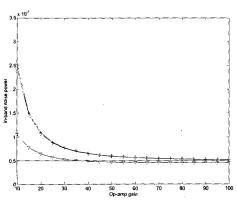

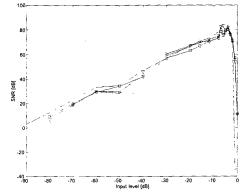

Figure 5. In-band noise power as a function of op-amp gains for a CT modulator:  $\nabla$  - first stage,  $\diamond$  - second stage, + - third stage, no markers - ideal case.

In Figure 4 the value of the above integral is plotted as a function of op-amp gain in different integrating stages for a third order SC modulator with oversampling ratio R=64, having a CIFB topology [6] and a Butterworth type noise transfer function. The plot in Fig. 5 depicts the same characteristic for a continuous-time modulator with the same parameters. One can easily see that the in-band noise power is larger in the case of SC modulators compared to continuous-time ones due to the additional effect of finite op-amp gains on SC integrator gains.

The drop in SNR due to the finite gain of op-amps is given by

$$\delta_{SNR} = 10 \log_{10} \left( \frac{P_e}{\tilde{P}_e} \right). \tag{13}$$

By numerically evaluating this quantity for different sets of op-amp gains and requiring a maximum drop of 3dB (1/2 LSB), the necessary values of op-amp gains can be determined. Multiple sets of gains can be obtained and the final decision should be made taking into account other constraints.

### 4. RESULTS AND CONCLUSIONS

We will consider next a third order  $\Delta\Sigma$  modulator with a CIFB (cascade of integrators with distributed feedback) topology as in Fig. 6. The results presented herein can be extended to any other order and topology.

Figure 6. CIFB topology for  $\Delta\Sigma$  modulators

For this structure the frequency response of the noise transfer function has been evaluated for the ideal case (infinite gain op-amps) and for both SC and CT realizations with finite gain op-amps. Computing the in-band noise power for op-amp gains taking values between 10 and 100, and requiring that  $\delta_{SNR} < 3dB$ , numerous sets of admissible values were obtained. From all these possibilities, we chose the minimum values satisfying the imposed SNR drop. However, a large number of value sets are still remaining and we have to consider some other rules to restrict the possible choices. Taking into account that the intrinsic noise of op-amps has a major role in decreasing the SNR of the delta-sigma modulator, and the contribution of each of the integrating stages is diminished by the gain of the preceding ones, the gains of the op-amps should be distributed in decreasing order from the first stage to the last one. This way, the noise requirements for the second to final stages are eased. Using this rule, the sets of minimum gain values from Table 1 for the three op-amps/OTAs have been obtained.

Table 1

| SC case  |          |          | $G_m - C$ case |          |          |

|----------|----------|----------|----------------|----------|----------|

| $1^{st}$ | $2^{nd}$ | $3^{rd}$ | $1^{st}$       | $2^{nd}$ | $3^{rd}$ |

| stage    | stage    | stage    | stage          | stage    | stage    |

| 75       | 70       | 30       | 70             | 50       | 25       |

| 70       | 50       | 35       | 55             | 55       | 25       |

| 55       | 55       | 35       | 50             | 40       | 30       |

| 55       | 45       | 40       | 45             | 45       | 30       |

| 50       | 50       | 40       | 45             | 35       | 35       |

| 45       | 45       | 45       | 40             | 40       | 35       |

Nevertheless, in the case of continuous-time  $G_m - C$  realizations, the linearity of the OTAs plays an important role. The most critical stage from this point of

view is the first one. Since for the same power consumption, the linear range of a transconductor is large if its transconductance is small, the gain of the OTA in the first integrating stage should be chosen the smallest possible to maximize its linear range. Thus, from the linearity point of view, the gains of op-amps should be chosen in decreasing order from the first stage to the final one, yielding the values from Table 2. One can easily see from both tables that indeed, in the case of continuous-time implementation, the minimum values for the necessary gains are smaller than the corresponding ones in the case of a SC realization.

Table 2

| SC case  |          |          | $G_m - C$ case |          |          |

|----------|----------|----------|----------------|----------|----------|

| $1^{st}$ | $2^{nd}$ | $3^{rd}$ | $1^{st}$       | $2^{nd}$ | $3^{rd}$ |

| stage    | stage    | stage    | stage          | stage    | stage    |

| 40       | 45       | 45       | 35             | 35       | 40       |

| 40       | 40       | 55       | 30             | 40       | 40       |

| 35       | 45       | 50       | 30             | 35       | 45       |

| 35       | 40       | 60       | 30             | 30 .     | 55       |

| 35       | 35       | 75       | 25             | 40       | 45       |

| 30       | 50       | 55       | 25             | 35       | 50       |

| 30       | 45       | 60       | 25             | 30       | 70       |

| 30       | 40       | 70       | 25             | 45       | 50       |

| 25       | 55       | 60       | 20             | 40       | 60       |

| 25       | 50       | 70       | 20             | 35       | 75       |

| 25       | 45       | 80       | 15             | 60       | 65       |

| 20       | 70       | 75       | 15             | 55       | 75       |

| 20       | 65       | 80       | 15             | 50       | 85       |

| 20       | 60       | 90       |                |          |          |

To validate the results obtained only by evaluating the in-band noise power based on the linear model of the quantizer, numerous direct simulations of the  $\Delta\Sigma$  modulators have been carried out. Figures 7 and 8 are presenting the SNR of the ideal modulators (infinite gain op-amps) and of the modulators for which three sets of the values in Table 2 for the gains of the op-amps were considered. It can be easily seen that the drop in the SNR is around 3 dB for all the studied cases. The final decision for the set of op-amp gains to be used in a practical implementation should consider additional constraints.

# 5. REFERENCES

- B. E. Boser and B. A. Wooley, The design of Sigma-Delta modulation analog-to-digital converters, IEEE J. Solid-State Circuits, vol. 23, no. 6, Dec. 1988, pp. 1298-1308.

- [2] S. Rabii and B. A. Wooley, The design of low-voltage, low-power sigma-delta modulators, Kluwer, 1999.

- [3] K. Martin and A. S. Sedra, Effects of the op amp finite gain and bandwidth on the performance of switched-capacitor filters, IEEE Trans. Circ. and Syst., vol. CAS-28, no. 8, Aug. 1981, pp. 822-829.

- [4] K. Nagaraj, K. Singhal, T. R. Viswanatahan, and J. Vlach, Reduction of finite-gain effect in switchedcapacitor filters, Electronics Letters, vol. 21, no. 15, July 1985, pp. 644-645.

- [5] R. Schreier and B. Zhang, Delta-Sigma modulators emplying continuous-time circuitry, IEEE Trans. Circ. Syst. - Part I, vol. 43, no. 4, April 1996, pp. 324-332.

- [6] S. R. Norsworthy, R. Schreier, and G. C. Temes (Eds.), Delta-Sigma data converters: Theory, design, and simulation, IEEE Press, 1997.

Figure 7. SNR vs input level for ideal SC modulator (no markers) and for three sets of op-amp gains in Table 2

Figure 8. SNR vs input level for ideal CT modulator (no markers) and for three sets of op-amp gains in Table 2